http://www.cpu-world.com/news_2014/2014061301_Some_details_of_Intel_Broadwell-DE_processors.html

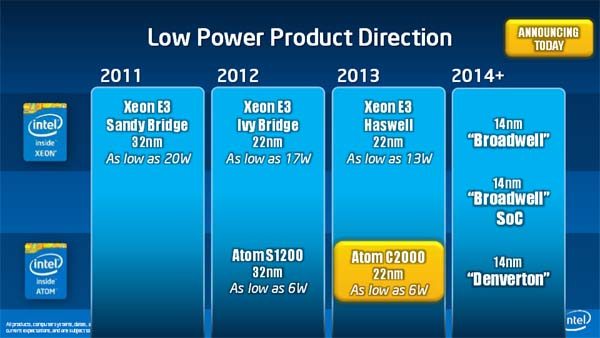

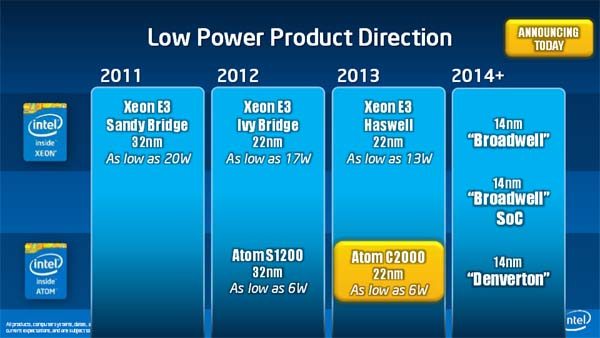

The latter systems on a chip will be a part of Grangeville platform for storage and communications, as well as for microservers markets. The SoCs, codenamed “Broadwell-DE”, will integrate not only “Broadwell” CPU cores and a memory controller, but also an I/O block and Platform Controller Hub (PCH) logic. We do not have verified information about the core count, however a SoC block diagram, that we have seen, shows 8 cores. Each core has 1.5 MB of L3 cache, as a result an 8-core processor should have 12 MB of L3 cache. The cores support most of Broadwell technologies, including Hyper-Threading, Turbo Boost, VT-x and VT-d virtualization, and Trusted Execution. Broadwell-DE parts for storage and communications also support QuickData technology 3.3. The processors have AES and AVX2 extensions enabled. New features in SoCs are Processor Trace (can capture details of code execution), supervisor mode access prevention, and extensions to ADC instruction.

Broadwell-DE chips incorporate a dual-channel memory controller, that supports DDR3L memory with data rates up to 1600 MHz, and DDR4 memory with data rates up to 2133 MHz, and up to 2400 MHz on some SKUs. Each channel supports up to 2 DIMMs, which allows the SoC to address up to 128 GB of RAM when 32GB DIMMs are used.

The I/O block includes 10 Gigabit Ethernet controller and 24 lanes of PCI-Express 3.0 interface. Furthermore, the on-chip PCH has 8 lanes of PCI-Express 2.0 interface, and 1Gb Ethernet controller. The PCH also provides 6 ports of SATA 6GB/s, 4 ports of USB 3.0 and 4 ports of USB 2.0.

The SoCs will be manufactured in a BGA package.